### **IJRAR.ORG**

E-ISSN: 2348-1269, P-ISSN: 2349-5138

## INTERNATIONAL JOURNAL OF RESEARCH AND **ANALYTICAL REVIEWS (IJRAR) | IJRAR.ORG**

An International Open Access, Peer-reviewed, Refereed Journal

# Review of modelling of surface potential for channel and gate engineered MOSFETs in subthreshold regime

<sup>1</sup>Swapnadip De, <sup>2</sup>Debasmita Ghosh, <sup>3</sup>Debjani Satpati

<sup>1</sup>Associate Professor, <sup>2</sup>Student, <sup>3</sup>Student <sup>1</sup>Department of Electronics and Communication Engineering <sup>1</sup>Meghnad Saha Institute of Technology, Kolkata, India

Abstract: In this work a review of modelling of subthreshold surface potential for short channel, LAC, Double halo and Double gate MOSFETs are carried out. The models are plotted using MATLAB. It is found that the results tally well with the models and simulation results from existing literatures.

*Index Terms* – Subthreshold surface potential, channel engineering, gate engineering

#### I. INTRODUCTION

It is found that the channel and gate engineering techniques, as well as Double gate MOSFETs suppress short channel effects effectively as in [1]-[6]. Here for double material gate two laterally contacted materials of different work functions are used. In the channel of MOSFET two different materials  $M_1$  and  $M_2$  with lengths  $L_1$  and  $L_2$ , and with work functions are  $\Phi_1$  and  $\Phi_2$ respectively, contacted laterally are used as the gate. The overall effective channel length L=L<sub>1</sub>+L<sub>2</sub> is defined as the distance from the source-channel metallurgical junction to the drain-channel metallurgical junction. The work function of the metal gate 1  $(M_1)$ is greater than that of metal gate 2 ( $M_2$ ), that is,  $\Phi_1 > \Phi_2$  for n-channel MOSFET. This gives rise to a step change of the surface potential profile at the point where M<sub>1</sub> and M<sub>2</sub> are contacted. The potential distribution introduces an additional peak field inside the channel resulting in a reduction of the field at the drain end. Thus the device immunity to the hot carrier effect is also increased.

An analytical model for the sub thershold surface potential in a short channel MOS transistor is developed by solving a pseudo-2D Poisson's equation, formulated by applying Gauss's law around a rectangular box in the channel depletion region. This model uses a physically based non-uniform depletion layer depth along the channel incorporating the role of channel length (L) and junction depth  $(x_i)$ , substrate doping  $(N_a)$ , oxide thickness  $(t_{ox})$ , and bias voltages in determining the surface potential.

#### **II Model description**

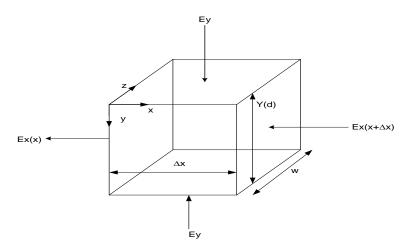

Only the 2-D analysis in the channel can provide accurate results. The analytical solution of the 2-D Possoin's equation is futher very complicated. Here Gauss's Law is applied to a recatngular box covering the total depletion layer depth. For Double gate MOSFET, At a given x, such an elementary Gaussian surface of length  $\Delta x$  covering the entire depletion width  $y_d$  is shown in Fig 1.1 where W is the gate width. Since the region outside the depletion layer is neutral, the vertical field  $E_{y2}$  on the bottom or back side and on the top or front side surface, E<sub>y1</sub> along the y direction is not zero here. So E<sub>y1</sub> and E<sub>y2</sub> can be obtained from the potential balanced equation:

$V_{gbf} = V_{fbf} + \psi_s + \psi_{ox}$  and the bottom side  $V_{gbb} = V_{fbb} + \psi_s + \psi_{ox}$  where  $\psi_s =$  Surface potential drop from surface to bulk outside the depletion region,  $\psi_{ox}$  = The potential drop across the oxide.  $V_{gbf}$  is the front gate bias voltage,  $V_{gbb}$  is the back gate bias voltage and  $V_{\text{fbf}}$  and  $V_{\text{fbb}}$  are the flat band voltage under front gate and back gate.

Fig:1.1: Gaussian surface

The flux line terminating on the interface charge per unit area  $Q_0$  will not contribute to the same since it is modeled as the effective interface charge which resides on the oxide side of the interface. Only flux lines terminating on Qc will contribute to the same and for an oxide thickness of  $t_{ox}$ , the corresponding vertical field can be obtained as:

$$E_{y1} = \frac{v_{gbf} - v_{fbf} - \psi_s}{t_{ox}} \qquad \qquad \text{and} \qquad \qquad E_{y2} = \frac{v_{gbb} - v_{fbb} - \psi_s}{t_{ox}}$$

In week inversion, the inversion layer charge can be ignored. For a substrate doping of a  $N_a$ , the total depletion charge due to the ionized acceptor atoms within the Gaussian surface is given by  $-q N_a \Delta x y_d W$  here q is the electronic charge. Therefore if the dielectric permittivity of the medium is  $\epsilon$  the mobile charge carriers are ignored, then after application of Gauss's law to the said surface, we get the following equation

$$\varepsilon \oint_{\text{surface}} \vec{E} \cdot \vec{ds} = -q N_a y_d \Delta x W$$

The left, right, top and bottom surface of the Gaussian box will have non-zero contribution to the left side of the integration.  $\varepsilon_{si}$  silicon and  $\varepsilon_{ox}$  SiO<sub>2</sub> respectively, can be expanded to

$$- \epsilon_{ox} E_{v1} \Delta x W + \epsilon_{ox} E_{v2} \Delta x W + \epsilon_{si} \left\{ -E_x(x + \Delta x) + E_x(x) \right\} y_d W = -q N_a \Delta x y_d W$$

So this equation can be written as

$$-\epsilon_{ox^*} \left\{ \; (V_{gbf^-}V_{fbf^-}\psi_s)/t_{ox} \right\} \; W + \epsilon_{ox^*} \left\{ \; (V_{gbb^-}V_{fbb^-}\psi_s) \; /t_{ox} \right\} \; \Delta x \; W + \; \epsilon_{si} \left\{ E_x(x + \Delta x) + E_x(x) \right\} \; \; y_dW \; = \; -q \; N_a \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; W \; = \; -q \; N_b \; \Delta x \; y_d \; = \; -q \; N_b \; \Delta x \; y_d \; = \; -q \; N_b \; \Delta x \; X_d \; = \; -q \; N_b \; \Delta x \; X_d \; = \; -q \; N_b \; \Delta x \; X_d \; = \; -q \; N_b \; \Delta x \; X_d \; = \; -q \; N_b \; \Delta x \; X_d \; = \; -q \; N_b \; \Delta x \; X_d \; = \; -q \; N_b \; \Delta x \; X_d \; = \; -q \; N_b \; \Delta x \; = \; -q \; N_b \; \Delta x \; = \; -q \; N_b \; \Delta x \; = \; -q \; N_b \; \Delta x \; = \; -q \; N_b \; \Delta x \; = \; -q \; N_b \; \Delta x \; = \; -q \; N_b \; \Delta x \; = \; -q \; N_b \; \Delta x \; = \; -q \; N$$

So ,

$$-\varepsilon_{si}*(d^2\psi_s/dx^2)-(c_{ox}/y_d)\psi_s = qN_a-(c_{ox}/y_d)(V_{gbf}-V_{fbb})-(c_{ox}/y_d)(V_{gbf}-V_{fbb})$$

or,

$$-\varepsilon_{si}*(d^2\psi_s/dx^2)-(c_{ox}/y_d)\psi_s = qN_a-(c_{ox}/y_d)V'_{gsf}-(c_{ox}/y_d)V'_{gsb}$$

or,

$$-\varepsilon_{si}*(d^2\psi_s/dx^2)-(c_{ox}/y_d)\psi_s = qN_a-(c_{ox}/y_d)(V'_{gsf}-V'_{gsb})$$

(1)

Left, right, top, bottom surface of Gaussian box are non zero. But in this case  $E_x$  is directed along the negative x direction.

where

$$V'_{gsf} = V_{gsf} + V_{sb} - V_{fbf}$$

and  $V'_{gsb} = V_{gsb} + V_{sb} - V_{fbb}$

$V_{gsf} / V_{gsb}$ = Front / back Gate to source voltage,  $V_{sb}$ =Source bias voltage,

V<sub>fbf</sub>/V<sub>fbfb</sub>= Front and back Flat band voltage under the front and back Gate the Mosfet.

For double metal gate MOSFET

$\Phi_{M1}$ = Work function of metal 1(M<sub>1</sub>),  $\Phi_{M2}$ = Work function of metal 2 (M<sub>2</sub>)

Here in halo region Flat band voltage  $V_{fbp} = -(E_g/2q) - \Phi_t \ln(N_p/n_i), \quad \text{where} \qquad \quad \Phi_t = kT/q$

$\Phi_{\rm t}$  is the thermal voltage,

n<sub>i</sub> the intrinsic carrier density,

N<sub>p</sub> halo doping concentration

E<sub>g</sub> the band gap in silicon=1.1ev

Flat band voltage of P-type substrate  $\Phi_{\text{fn}} = \Phi_{\text{t}} \ln(N_a/n_i)$ ,

N<sub>a</sub>= p- type substrate doping concentration,

y<sub>d</sub> is the depletion layer depth under the gate,

Fig: 1.2 DGDHDM MOSFET structure

For short channel Double gate double pocket double metal MOSFET , the contribution of two junction regions and for two different metal gate and two halo doping, which causes a non uniformity to  $y_d$  . so surface potential depends on depletion layer thickness which is not constant for this model. So  $y_d(x)$  be modeled first for an accurate prediction of the surface potential. If the channel length is not too small and reasonable amount of voltage is applied to source and drain,  $y_d(x)$  is typically varying with x. Unfortunately, the depletion layer depth around the source and drain junctions is a complex function of substrate doping, junction depth, and drain and source bias voltages. So flat band voltage under metal 1 of gate is  $V_{fb1}=(\Phi_{M1}-\Phi_s)/q$ , and Flat band voltage under metal 2 of gate is  $V_{fb2}=(\Phi_{M2}-\Phi_s)/q$ . where work function of silicon substrate is

$\Phi_s\!\!=\!\!(E_g/\,2q)+\Phi_f+\,\,\chi$  , where  $\chi$  is the electron affinity of silicon,

$C_{ox} = \epsilon_{ox}/t_{ox}$  is the oxide capacitance per unit gate area,  $t_{ox}$  is the gate oxide thickness  $\epsilon_{si}$  and  $\epsilon_{ox}$  are the dielectric permittivity of Si and SiO<sub>2</sub> respectively. To predict  $\Psi$ s accurately, an appropriate model for  $y_d(x)$ . If the effect of the source and drain junction depletion regions neglected, it can be expressed as

$$v_d = (2\varepsilon_{si} \Psi_s/qN_a)^{1/2}$$

, where  $\Psi_s = (\gamma /2 + (\gamma^2 /4 + V_{gb} - V_{fb})^{1/2})^2$

is the gate-controlled sub threshold surface potential for a long channel MOSFET, and

$\gamma = (2q \, \epsilon_{si} N_a)^{1/2} / C_{ox}$  is the body effect co-efficient.

different  $y_d$  results (  $y_{(d)1}$ ,  $y_{(d)2}$ ,  $y_{(d)3}$ ,  $y_{(d)4}$ ) because of four different flat band voltage  $V_{fbp1}$ ,  $V_{fb1}$ ,  $V_{fb2}$  and  $V_{fbp2}$  due to  $M_1$ ,  $M_2$  and both side halo region but difference of flat band voltage under the Front gate and Back gate. Considering the typical variation of  $y_d(x)$  with x near the source and drain junctions, we use a physically based simple and approximate model for it as  $y_d(x) = (ax + b)^2$ . The channel is then divided into six regions, and in all the regions, the depletion layer depth is modeled as  $y_d(x) = (ax + b)^2$  in equation 1.

so

$$(ax + b)^2 \frac{d^2 \Psi_s}{dx^2} - \frac{c_{ox}}{c_{si}} \Psi_s = \frac{qN_a}{\epsilon_{si}} (ax + b)^2 - \frac{c_{ox}}{\epsilon_{si}} (V'_{gsf} - V'_{gsb})$$

(2)

Based on the channel length, pocket length, doping concentration, and applied voltages, two cases for the six regions are required to be considered under the boundary values of potential

At  $x_1=0$  position of the channel length voltage  $V_1=V_{bi}+V_{sb}$

At  $x_7 = L$ , position of the channel length voltage  $V_7 = V_{bi} + V_{db}$

Where  $V_{bi}$ = Built in potential,  $V_{bi}$ =  $(E_g/2q)+\Phi_{fp}$ , and when  $\Phi_{fbp}=\Phi_t \ln(N_p/n_i)$ , Fermi potential of p-type substrate,  $\Phi_t=kT/q$  the thermal voltage,  $n_i$  is the intrinsic carrier density, and  $V_{ds}$  is the drain-to-source bias.

Using the substitution  $t = \ln (ax+b)$ , dt/dx = a/(ax+b) .we can solve (equ<sup>n</sup> 1) for  $\Psi_s$  as given below for the various regions, D = d/dt, so we can write

$$(ax+b)^2 \frac{d^2\Psi_g}{dv^2} = a^2 D(D-1)\Psi$$

(3)

© 2024 IJRAR July 2024, Volume 11, Issue 3 So, d=  $\sqrt{(1/2)^2}$  +  $(C_{ox}/$   $\epsilon_{si}a^2)$ , and  $C_1$ and c<sub>2</sub> are the arbitrary constant, so complementary

$$CR = e^{\frac{t}{2}} \left( C_1 e^{dt} + C_2 e^{-dt} \right) \text{ , } \beta = q N_a / \left( 2 \, \epsilon_{si} a^2 - C_{ox} \right) \text{, so particular integral is PI} = \beta e^{2t} + \left( V'_{\text{gsf}} - V'_{\text{gsb}} \right)$$

So for Front gate flat band voltage under halo and material 1 is  $V_{fbpf1}=V_{fbfp}-V_{fbf1}$ ,

for back gate flat band voltage under halo and material 1  $\,$  is  $\,$   $V_{fbpb1} = V_{fbbp} - V_{fbb1},$

for Front gate flat band voltage under halo and material 2 is  $V_{fbpf2}=V_{fbfp}-V_{fbf2}$ ,

for back gate flat band voltage under halo and material 2  $is V_{fbpb2}=V_{fbbp}-V_{fbb2}$

#### IV. RESULTS AND DISCUSSION

In this work subthreshold surface potential of short channel and Channel and gate engineered Double Gate MOSFETs are obtained using MATLAB.

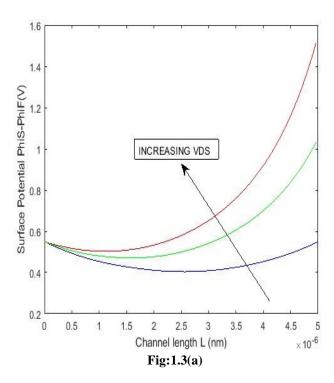

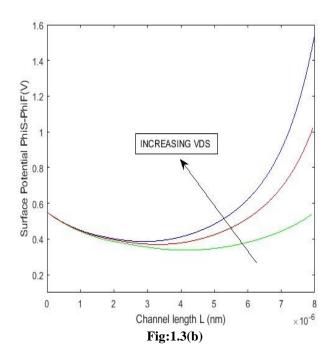

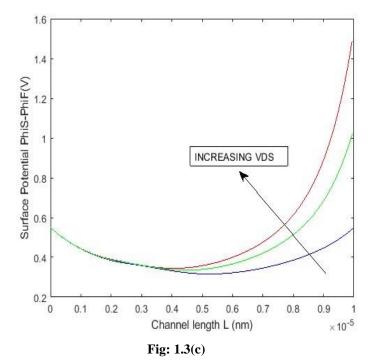

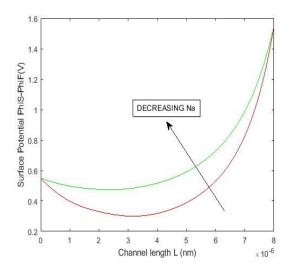

Fig 1.3(a,b,c) Plot of subthreshold surface potential vs channel length for L=50 ,80 and 100nm considering Na =  $4*10^17$  cm<sup>3</sup>-3

Fig 1.4 Plot of surface potential vs channel length considering Na=10^18 and 2\*10^17 cm^-3

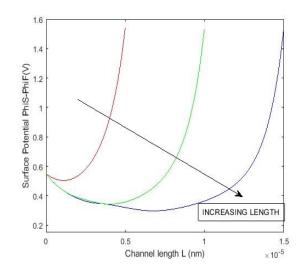

Fig 1.5 Plot of surface potential vs channel length considering L=50 ,100,150 nm

The DGDMDH structure uses a relatively lower doped substrate than halo region in the channel. The high Work function near the source leads to more rapid acceleration of carriers in the channel and the low Work function near the drain leads to reduction of peak electric field at the drain side.

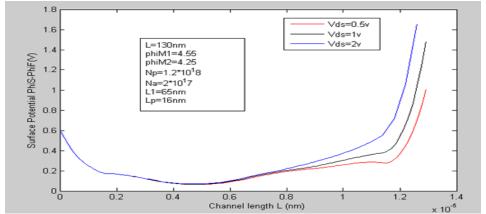

Fig:1.6 (a) Surface potential v/s channel length plot for  $V_{ds} = 0.5V$ , 1V, 2V in L= 130 nm

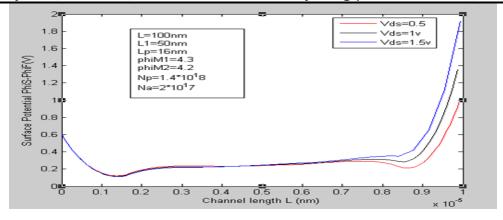

Fig :1.6 (b) Surface potential v/s channel length plot for  $V_{ds} = 0.5V$ , 1V and 1.5V in L=100 nm

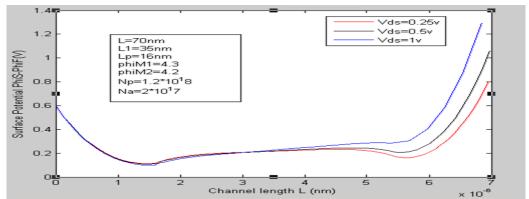

Fig:1.6(c) Surface potential v/s channel length plot for V<sub>ds</sub> =0.25V, 0.5V, 1V in L=70 nm

It is seen that as the drain-to-source voltage is increased, then the depletion depth increases and the inversion charge increases and the

#### V. CONCLUSION

The surface potential is the most important parameter which needs to be found for any device. In this thesis Double Gate Dual Material Double Halo structure, combining the channel and gate engineering technique to double gate MOSFET is proposed. Some existing literature used simulation to show that Single Halo Dual Material Double Gate structure suppresses short channel effects more effectively than halo or DMG MOSFETs. An analytical expression of surface potential in sub threshold region is formulated by applying Gauss's law to a rectangular box in the channel, covering the entire depletion depth. This method eliminates the need of solving complex Poisson's equation in the channel.

#### REFERENCES

- [1] S.Baishya, A.Mallik and C. K. Sarkar, "A subthreshold surface potential model for short-channel MOSFET taking into account the varying depth of channel depletion layer due to source and drain junctions", IEEE Trans. Electron Devices, vol. 53,pp. 507-514, Mar. 2006.

- [2] S. Baishya, A. Mallik and C. K. Sarkar, "A subthreshold surface potential and drain current model for lateral asymmetric channel (LAC) MOSFETs", IETE Journ-al of Research, vol. 52, pp. 379 390, Sept-Oct. 2006.

- [3] S. Baishya, A. Mallik and C. K. Sarkar, "Subthreshold surface potential and drain current models for short-channel pocket implantedMOSFETs", Microele-ctronics Engineering. Available online.

- [4] M. Saxena, S. Haldar, M. Gupta, et al, "Design considerations for novel device architecture: hetero-material double-gate (HEM-DG) MOSFET with sub-100 nm gate length," Solid- State Electronics, vol. 48, no. 7, pp. 1167-1174, 2004

- [5] "Investigation of novel attributes of single halo dual-material double gate MOSFETs for analog/RF applications" N. Mohankumar \*, Binit Syamal, C.K. Sarkar Department of Electronics and Communication Engineering, Jadavpur University, Kolkata 700 032, India Article history: Received 14 November 2008

- [6] S. Baishya, A. Mallik and C. K. Sarkar, "A Pseudo Two-Dimensional Subthreshold surfa-ce potential model for Dual-Material Gate MOSFETs", IEEE Trans. Electron Devices, vol. 54, pp. 2520-2525, Sept. 2007